## Si2107/08/09/10

# SATELLITE RECEIVER FOR DVB-S/DSS WITH QUICKLOCK AND QUICKSCAN

#### **Features**

- Single-chip tuner, demodulator, and LNB controller

- DVB-S- and DSS-compliant

- QPSK/BPSK demodulation

- Integrated step-up dc-dc converter for LNB power supply (Si2108/10 only)

- Input signal level: -82 to -10 dBm

- Symbol rate range:1 to 45 MBaud

- Automatic acquisition and fade recovery

- Automatic gain control

- On-chip blind scan accelerator with QuickScan (Si2109/10 only)

- DiSEqC™ 2.2 support

- Power, C/N, and BER estimators

- I<sup>2</sup>C bus interface

- 3.3/1.8 V supply, 3.3 V I/O

- Pb-free/RoHS-compliant package

## Applications

- Set-top boxes

- Digital video recorders

- Digital televisions

- Satellite PC-TV

- SMATV trans-modulators (Satellite Master Antenna TV)

#### Pin Assignments Si2107/08/09/10 ℩ REXT 2 ADDR 3 34 XTAL2 33 VDD\_XTAL VDD\_MIX 4 (32) XTOUT VDD\_BB 5 (31) VDD\_PLL33 Top VDD\_ADC 6 [30] INT/RLK/GPO VSEN/TDET 7 29 TS\_ERR View LNB1/TGEN 8 ISEN 9 TS\_SYNC LNB2/DRC 10 (26) SDA RESET [11] 25 SCL PWM/DCS 1121 [24] TS\_DATA[7] GND VDD\_DIG18 13 23 TS\_DATA[6] 4 6 6 7 6 6 2 2 2

#### **Description**

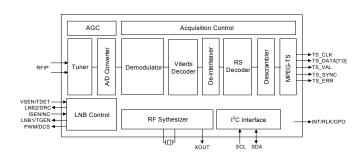

The Si2107/08/09/10 are a family of pin-compatible, complete front-end solutions for DSS and DVB-S digital satellite reception. The IC family incorporates a tuner, demodulator, and LNB controller into a single device resulting in significantly reduced board space and external component count. The device supports symbol rates of 1 to 45 MBaud over a 950 to 2150 MHz range. A full suite of features including automatic acquisition, fade recovery, blind scanning, performance monitoring, and DiSEqC Level 2.2 compliant signaling are supported. The Si2108/10 further add short circuit protection, overcurrent protection, and a step-up dc-dc controller to implement a low-cost LNB supply solution. Si2109/10 versions include a hardware channel scan accelerator for fast "blindscan". The Si2107/08/09/10 family features new channel detection and acquisition technology: *QuickLock* for Si2107/08/09/10 and *QuickScan* for Si2109/10. *QuickLock* achieves fast channel acquisition and *QuickScan*, fast channel detection. An I<sup>2</sup>C bus interface is used to configure and monitor all internal parameters.

#### **Functional Block Diagram**

## TABLE OF CONTENTS

| <u>Section</u>                                                | <u>Page</u> |

|---------------------------------------------------------------|-------------|

| 1. Electrical Specifications                                  | 4           |

| 2. Typical Application Schematics                             |             |

| 3. Bill of Materials                                          |             |

| 4. Part Versions                                              |             |

| 5. Functional Description                                     | 20          |

| 5.1. Tuner                                                    |             |

| 5.2. Demodulator                                              |             |

| 5.3. DVB-S/DSS Channel Decoder                                |             |

| 5.4. On-Chip Blindscan Controller: QuickScan (Si2109/10 Only) |             |

| 5.5. LNB Signaling Controller                                 |             |

| 5.6. On-Chip LNB DC-DC Step-Up Controller (Si2108/10 Only)    |             |

| 5.7. Crystal Oscillator                                       |             |

| 6. Operational Description                                    |             |

| 6.1. System Configuration                                     |             |

| 6.2. Interrupts                                               |             |

| 6.3. Receiver Status                                          |             |

| 6.4. Tuning Control                                           |             |

| 6.5. Channel Decoder                                          |             |

| 6.6. Automatic Gain Control                                   |             |

| 6.7. LNB Signaling Controller                                 |             |

| 6.8. On-Chip LNB DC-DC Step-Up Controller (Si2108/10 Only)    |             |

| 6.9. On-Chip Blindscan Controller: QuickScan (Si2109/10 Only) |             |

| 7. I <sup>2</sup> C Control Interface                         |             |

| 8. Control Registers                                          |             |

| 9. Pin Descriptions                                           |             |

| 10. Ordering Guide1,2                                         |             |

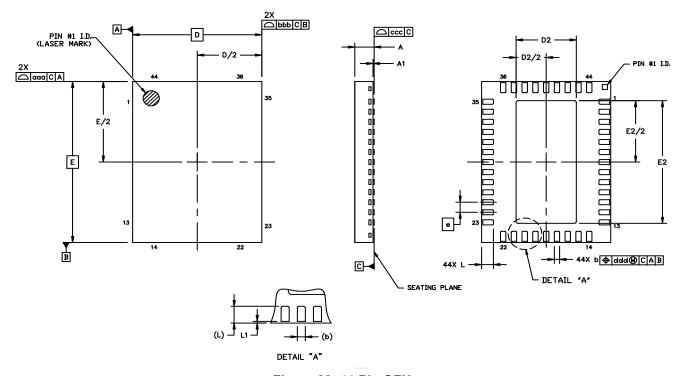

| 11. Package Outline: 44-pin QFN                               |             |

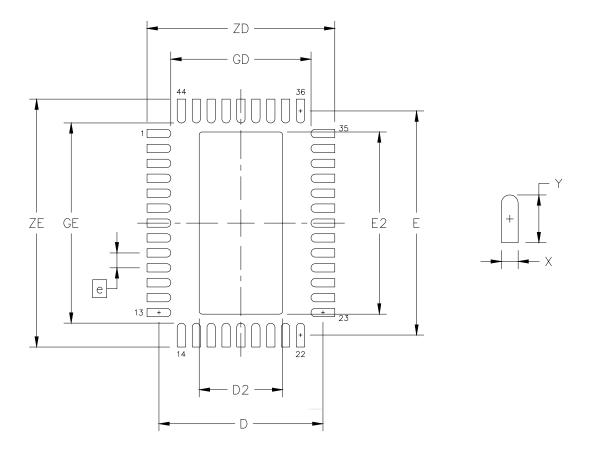

| 12. PCB Land Pattern                                          |             |

| Document Change List                                          |             |

| Contact Information                                           | 0.4         |

#### 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                                                                                                          | Symbol           | Min  | Тур | Max  | Unit |  |

|--------------------------------------------------------------------------------------------------------------------|------------------|------|-----|------|------|--|

| Ambient temperature                                                                                                | T <sub>A</sub>   | 0    | _   | 70   | °C   |  |

| DC supply voltage, 3.3 V                                                                                           | V <sub>3.3</sub> | 3.0  | 3.3 | 3.6  | V    |  |

| DC supply voltage, 1.8 V                                                                                           | V <sub>1.8</sub> | 1.71 | 1.8 | 1.89 | V    |  |

| Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. |                  |      |     |      |      |  |

Table 2. Absolute Maximum Ratings<sup>1, 2</sup>

| Parameter                           | Symbol           | Min         | Max                    | Unit |

|-------------------------------------|------------------|-------------|------------------------|------|

| DC supply voltage, 3.3 V            | V <sub>3.3</sub> | -0.3        | 3.9                    | V    |

| DC supply voltage, 1.8 V            | V <sub>1.8</sub> | -0.3        | 2.19                   | V    |

| Input voltage (pins 2, 3, 7, 9, 11_ | V <sub>IN</sub>  | -0.3        | V <sub>3.3</sub> + 0.3 | V    |

| Input current (pins 2, 3, 7, 9, 11) | I <sub>IN</sub>  | -10         | +10                    | mA   |

| Operating ambient temperature       | T <sub>OP</sub>  | -10         | +70                    | °C   |

| Storage temperature                 | T <sub>STG</sub> | <b>–</b> 55 | 150                    | °C   |

| RF input level                      |                  | _           | 10                     | dBm  |

| ESD protection (pins 1–44)          |                  | _           | 2                      | kV   |

#### Notes:

- 1. Permanent damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operations sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **2.** The Si2107/08/09/10 is a high-performance RF integrated circuit. Handling and assembly of these devices should only be done at ESD-protected workstations.

**Table 3. DC Characteristics**

$(V_{3.3} = 3.3 \text{ V} \pm 10\%, V_{1.8} = 1.8 \text{ V} \pm 10\%, T_A = 0-70 \text{ °C})$

| Parameter                  | Symbol           | Test Condition                                                 | Min | Тур | Max | Unit |

|----------------------------|------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Supply Current, 3.3 V      | I <sub>3.3</sub> | 45 Mbaud, CR 7/8 <sup>1</sup>                                  | _   | 313 | _   | mA   |

|                            |                  | 20 Mbaud, CR 2/3 <sup>1</sup>                                  | _   | 298 | _   | mA   |

| Supply Current, 1.8 V      | I <sub>1.8</sub> | 45 Mbaud, CR 7/8 <sup>1</sup>                                  | _   | 292 | _   | mA   |

|                            |                  | 20 Mbaud, CR 2/3 <sup>1</sup>                                  | _   | 217 | _   | mA   |

| Input high voltage         | V <sub>IH</sub>  | SCL(25), SDA(26)                                               | 2.3 | _   | 5.5 | V    |

| Input low voltage          | V <sub>IL</sub>  | SCL(25), SDA(26)                                               | 0   |     | 0.8 | V    |

| Input leakage <sup>2</sup> | Iı               | SCL(25), SDA(26),<br>RESET(11),<br>XTAL1(35), VSEN/<br>TDET(7) | _   | _   | ±10 | μА   |

| Output high voltage        | V <sub>OH</sub>  |                                                                | 2.4 | _   | _   | V    |

| Output low voltage         | V <sub>OL</sub>  |                                                                | _   | _   | 0.4 | V    |

| Output leakage             | l <sub>OL</sub>  |                                                                | _   | _   | ±10 | μA   |

| N1 4                       | *                | •                                                              |     | •   | •   |      |

#### **Notes**

- 1. LNB dc-dc converter disabled; LNB\_EN (CEh[2]) = 0.

- 2. ISEN(9) is not tested for leakage current.

#### **Table 4. RF Electrical Characteristics**

| Parameter                       | Symbol              | Test Condition             | Min | Тур              | Max        | Unit   |

|---------------------------------|---------------------|----------------------------|-----|------------------|------------|--------|

| Input power, single channel     | P <sub>i,ch</sub>   | washing at                 | _   | -82 <sup>1</sup> | -10        | dBm    |

| Aggregate input power           | P <sub>i,agg</sub>  |                            | _   | _                | <b>-</b> 7 | dBm    |

| Input impedance, balanced       | Z <sub>in</sub>     | $Z_{SOURCE} = 75 \Omega$   | _   | 75               | _          | Ω      |

| Return Loss                     |                     |                            | _   | -10              | _          | dB     |

| Dynamic voltage gain range      | $\Delta_{GV}$       |                            | _   | 75               | _          | dB     |

| Maximum voltage gain            | G <sub>V(max)</sub> |                            | _   | 55               | _          | dB     |

| Noise figure                    | NF                  | Max gain <sup>2</sup>      | _   | +9.5             | +12.5      | dB     |

| IP3                             | IP3 <sup>3</sup>    | Min gain <sup>2</sup>      | +5  | +15              | _          | dBm    |

| LO leakage                      | L <sub>LO</sub>     | 950 to 2150 MHz            | _   | _                | -70        | dBm    |

| LO SSB phase noise              | NI                  | 100 kHz offset             | _   | -97              | -94        | dBc/Hz |

| LO 33B phase hoise              | $N_{LO}$            | 1 MHz offset               | _   | -97              | -94        | dBc/Hz |

| LO DSB phase noise (integrated) | N <sub>LO</sub>     | 10 kHz to 1/2 Baud<br>Rate |     | 2.1              | 2.8        | °rms   |

| RF synthesizer spurious         |                     | At 20 MHz offset           | _   | -40              | _          | dBc/Hz |

| LO oscillator settling time     | t <sub>s,LO</sub>   |                            | _   | 100              | _          | μs     |

#### Notes:

- 1. For a single channel with SR = 27.5 Mbaud, CR = 7/8, and no added noise. Input power range over which bit error rate is less than 2e-4 after Viterbi decoder.

- 2. Max gain = 0hFFFF in AGC settings registers (25h–26h). Min gain = 0h0000 in AGC settings registers (25h–26h).

- 3. IM3 can be calculated as follows: IM3 =  $2 \times (IP3 P_{in})$ .

**Table 5. Receiver Characteristics**

| Parameter                                            | Symbol               | Test Condition                                     | Min | Тур  | Max  | Unit  |

|------------------------------------------------------|----------------------|----------------------------------------------------|-----|------|------|-------|

| Rf Input Frequency Range                             | f <sub>in</sub>      |                                                    | 950 | _    | 2150 | MHz   |

| Fine Tune Step Size                                  | f <sub>step</sub>    |                                                    | _   | 12.2 | _    | kHz   |

| Symbol Rate Range                                    | R <sub>S</sub>       |                                                    | 1   | _    | 45   | MBaud |

| Carrier Offset Correction Range                      | f <sub>car_off</sub> |                                                    | _   | ±6   | _    | MHz   |

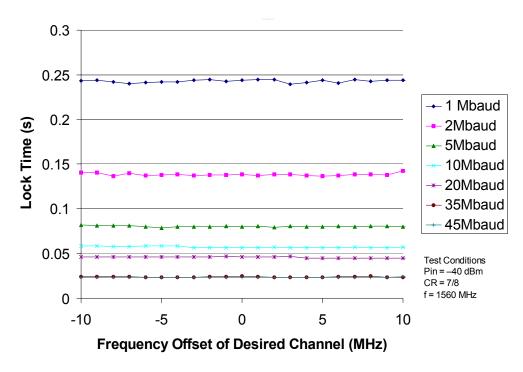

| Carrier Lock/Acquisition Times with <i>QuickLock</i> | TQL                  | 45 MBaud, CR = 7/8 Channel<br>Offset = ±5 MHz*     | _   | 0.02 | _    | Sec   |

|                                                      |                      | 27.5 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz* | _   | 0.03 | _    | Sec   |

|                                                      |                      | 20 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz*   | _   | 0.04 | _    | Sec   |

|                                                      |                      | 10 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz*   | _   | 0.05 | _    | Sec   |

|                                                      |                      | 5 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz*    | _   | 0.08 | _    | Sec   |

|                                                      |                      | 2 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz*    | _   | 0.14 | _    | Sec   |

|                                                      |                      | 1 MBaud, CR = 7/8, Channel<br>Offset = ±10 MHz*    | _   | 0.25 | _    | Sec   |

\*Note: For signal with C/N = 8.5 dB Pin = -40 dBm, Channel frequency = 1560 MHz.

Table 6. LNB Supply Characteristics (Si2108/10 Only)

| Parameter                                | Symbol              | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min   | Тур    | Max  | Unit      |

|------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------|-----------|

| Supply Voltage                           | V <sub>LNB_IN</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8     | 12     | 13.2 | V         |

| Converter Switch Frequency               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 237   | 264    | 290  | kHz       |

| Output HIGH voltage                      |                     | VHIGH = 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17.75 | 18.625 | 19.5 | V         |

| Output HIGH voltage                      |                     | VHIGH = 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17.0  | 18.0   | 19.0 | V         |

| Output I OW voltage                      |                     | VLOW = 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.75 | 13.375 | 14.0 | V         |

| Output LOW voltage                       |                     | VLOW = 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.5  | 13.25  | 14.0 | V         |

| Low to High Transition Time              |                     | 13 to 18 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _      | 1    | ms        |

| High to Low Transition Time              |                     | 18 to 13 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _      | 1    | ms        |

| Line Regulation                          |                     | $V_{CC} = 8 \text{ to}$<br>13.2 V<br>$I_{o} = 500 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _     | _      | 200  | ΔmV       |

| Load Regulation                          |                     | I <sub>o</sub> = 50 to<br>500 mA<br>V <sub>CC</sub> = 12 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _      | 200  | ΔmV       |

| Load Capacitance Tolerance               |                     | DiSEqC 1.x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _      | 0.75 | μF        |

|                                          |                     | DiSEqC 2.x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _      | 0.25 | μF        |

| Output current limiting                  |                     | ILIM = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 400   | _      | 550  | mA        |

|                                          |                     | ILIM = 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 500   | _      | 650  | mA        |

| Maximum LNB Supply Current               |                     | IMAX = 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.4   | 1.6    | 1.92 | Α         |

| Tone Frequency                           | f <sub>tone</sub>   | and the state of t | 20    | 22     | 24   | kHz       |

| Tone Amplitude                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 500   | 650    | 800  | mV        |

| Tone Duty Cycle                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40    | 50     | 60   | %         |

| Tone Rise and Fall Time                  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3     | 6      | 10   | μs        |

| Tone Detector Frequency Capture<br>Range |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17.6  | _      | 26.4 | kHz       |

| Tone Detector Input Amplitude            |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200   | _      | 1000 | $mV_{pp}$ |

| Note: Specifications based on recommen   | ded schematics      | in Figure 8 and Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e 9.  |        |      |           |

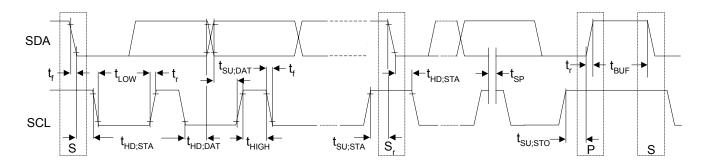

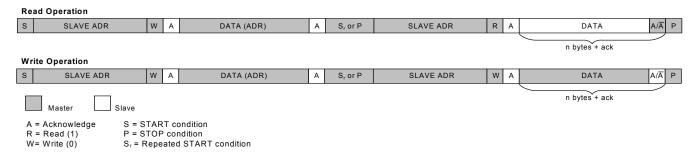

Table 7. I<sup>2</sup>C Bus Characteristics

| Parameter                                                                                      | Symbol                         | Test Condition | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----|-----|-----|------|

| SCL Clock Frequency                                                                            | f <sub>SCL</sub>               |                | 0   | _   | 400 | kHz  |

| Bus Free Time between START and STOP Condition                                                 | t <sub>BUF</sub>               |                | 1.3 | _   | _   | μs   |

| Hold Time (repeated) START Condition. (After this period, the first clock pulse is generated.) | t <sub>HD, STA</sub>           |                | 0.6 | _   | _   | μs   |

| LOW Period of SCL Clock                                                                        | t <sub>LOW</sub>               |                | 1.3 | _   | _   | μs   |

| HIGH Period of SCL Clock                                                                       | t <sub>HIGH</sub>              |                | 0.6 | _   | _   | μs   |

| Data Setup Time                                                                                | t <sub>SU, DAT</sub>           |                | 100 | _   | _   | ns   |

| Data Hold Time                                                                                 | t <sub>HD, DAT</sub>           |                | 0   | _   | 0.9 | μs   |

| SCL and SDA Rise and Fall Time                                                                 | t <sub>r,</sub> t <sub>f</sub> |                | _   | _   | 300 | ns   |

| Setup Time for a Repeated START Condition                                                      | t <sub>SU, STA</sub>           |                | 0.6 | _   | _   | μs   |

| Setup Time for STOP Condition                                                                  | t <sub>su,sto</sub>            |                | 0.6 | _   | _   | μs   |

| Capacitive Load for each Bus Line                                                              | C <sub>B</sub>                 |                | _   | _   | 400 | pF   |

Figure 1. I<sup>2</sup>C Timing Diagram

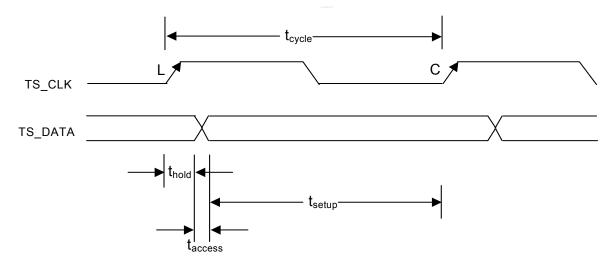

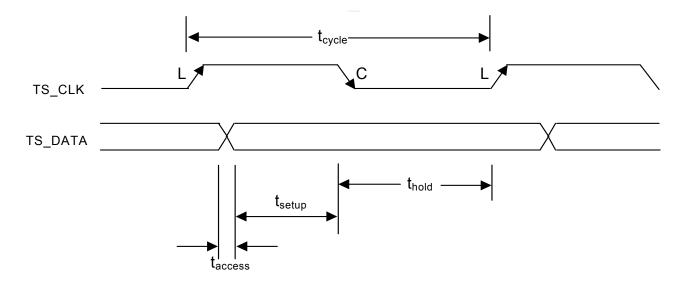

**Table 8. MPEG-TS Specifications (Rising Launch and Capture)**

| Parameter        | Symbol              | Test Condition           | Min  | Тур                      | Max  | Unit |

|------------------|---------------------|--------------------------|------|--------------------------|------|------|

| Clock cycle time | t <sub>cycle</sub>  | Serial mode              | 11.3 | _                        | 28.6 | ns   |

|                  |                     | Parallel mode            | 77   | _                        | 8000 | ns   |

| Clock low time   | t <sub>clow</sub>   | Serial mode (TSSCR = 11) | 5.1  | _                        | 6.9  | ns   |

|                  |                     | Serial mode (TSSCR = 00) | 12.0 | _                        | 15.8 | ns   |

|                  |                     | Parallel mode            | 39   | _                        | 4000 | ns   |

| Clock high time  | t <sub>chigh</sub>  | Serial mode (TSSCR = 01) | 5.1  | _                        | 6.9  | ns   |

|                  |                     | Serial mode (TSSCR = 11) | 12.0 | _                        | 15.8 | ns   |

|                  |                     | Parallel mode            | 39   | _                        | 4000 | ns   |

| Hold time        | t <sub>hold</sub>   | Normal operation         | _    | 0                        | _    | ns   |

|                  |                     | Data delayed (TSDD = 1)  | _    | 1.5                      | _    | ns   |

|                  |                     | Clock Delayed (TSCD = 1) | _    | -1.5                     | _    | ns   |

| Setup time       | t <sub>setup</sub>  | Normal operation         | _    | t <sub>cycle</sub> – 1.5 | _    | ns   |

|                  |                     | Data delayed (TSDD = 1)  | _    | t <sub>cycle</sub> - 3.0 | _    | ns   |

|                  |                     | Clock Delayed (TSCD = 1) | _    | t <sub>cycle</sub>       | _    | ns   |

| Access time      | t <sub>access</sub> |                          |      | 1.5                      | _    | ns   |

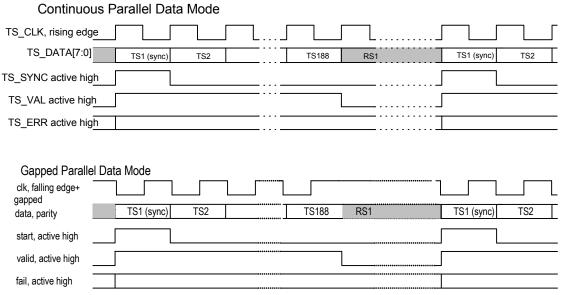

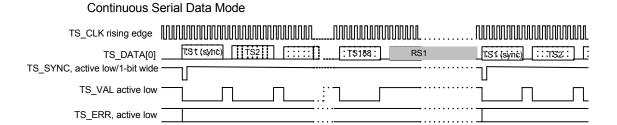

Figure 2. MPEG-TS (Rising Launch and Capture) Timing Diagram

**Table 9. MPEG-TS Specifications (Rising Launch, Falling Capture)**

| Parameter        | Symbol              | Test Condition           | Min  | Тур                         | Max  | Unit |

|------------------|---------------------|--------------------------|------|-----------------------------|------|------|

| Clock cycle time | t <sub>cycle</sub>  | Serial mode              | 11.3 | _                           | 28.6 | ns   |

|                  |                     | Parallel mode            | 77   | _                           | 8000 | ns   |

| Clock low time   | t <sub>clow</sub>   | Serial mode (TSSCR = 11) | 5.1  | _                           | 6.9  | ns   |

|                  |                     | Serial mode (TSSCR = 00) | 12.0 | _                           | 15.8 | ns   |

|                  |                     | Parallel mode            | 39   | _                           | 4000 | ns   |

| Clock high time  | t <sub>chigh</sub>  | Serial mode (TSSCR = 01) | 5.1  | _                           | 6.9  | ns   |

|                  |                     | Serial mode (TSSCR = 11) | 12.0 | _                           | 15.8 | ns   |

|                  |                     | Parallel mode            | 39   | _                           | 4000 | ns   |

| Hold time        | t <sub>hold</sub>   | Normal operation         | _    | t <sub>cycle</sub> /2       | _    | ns   |

|                  |                     | Data delayed (TSDD = 1)  | _    | t <sub>cycle</sub> /2 + 1.5 | _    | ns   |

|                  |                     | Clock Delayed (TSCD = 1) | _    | t <sub>cycle</sub> /2 - 1.5 | _    | ns   |

| Setup time       | t <sub>setup</sub>  | Normal operation         | _    | t <sub>cycle</sub> /2 - 1.5 | _    | ns   |

|                  |                     | Data delayed (TSDD = 1)  | _    | $t_{\text{cycle}}/2 - 3.0$  | _    | ns   |

|                  |                     | Clock Delayed (TSCD = 1) | _    | t <sub>cycle</sub> /2       | _    | ns   |

| Access time      | t <sub>access</sub> |                          | _    | 1.5                         | _    | ns   |

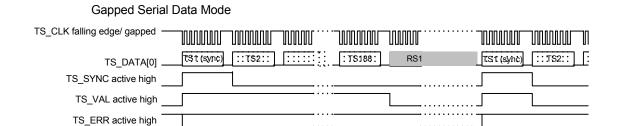

Figure 3. MPEG-TS (Rising Launch, Falling Capture) Timing Diagram

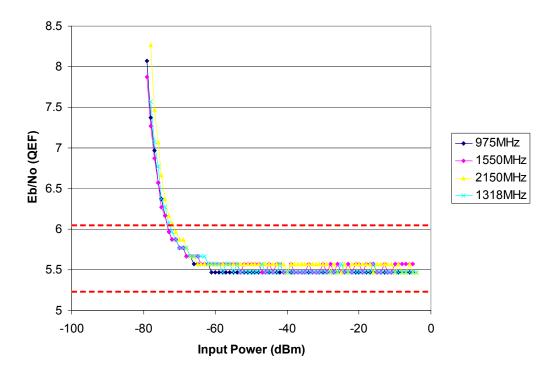

Figure 4. Eb/No (QEF Operation) vs. Input Power for Si2107/08/09/10 (Typical) SR = 27.5 MBaud, CR = 7/8

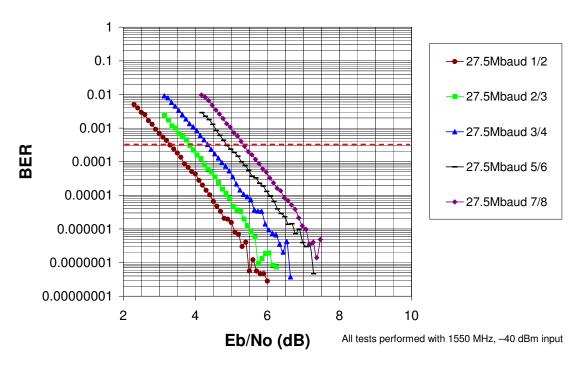

Figure 5. BER After Viterbi vs. Eb/No for Si2107/08/09/10

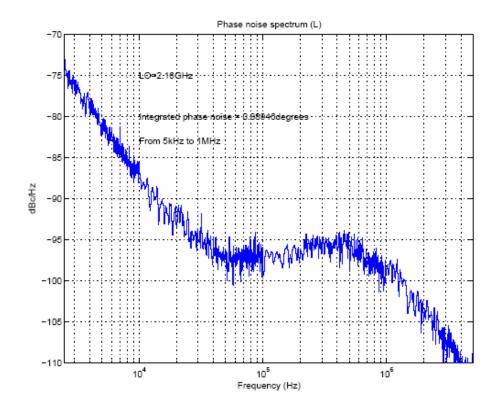

Figure 6. Phase Noise Performance for Si2107/08/09/10 (Typical)

Figure 7. Frequency Offset vs. Carrier Lock/Acquisition Time for Various Baudrates Using *QuickLock* (Typical)

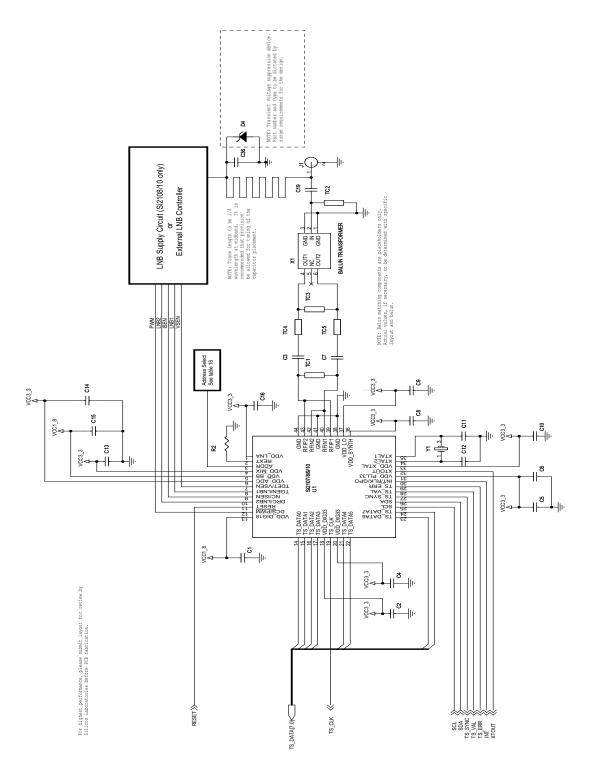

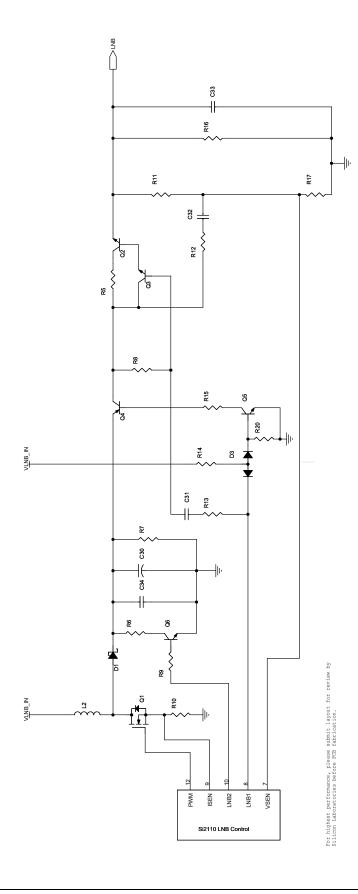

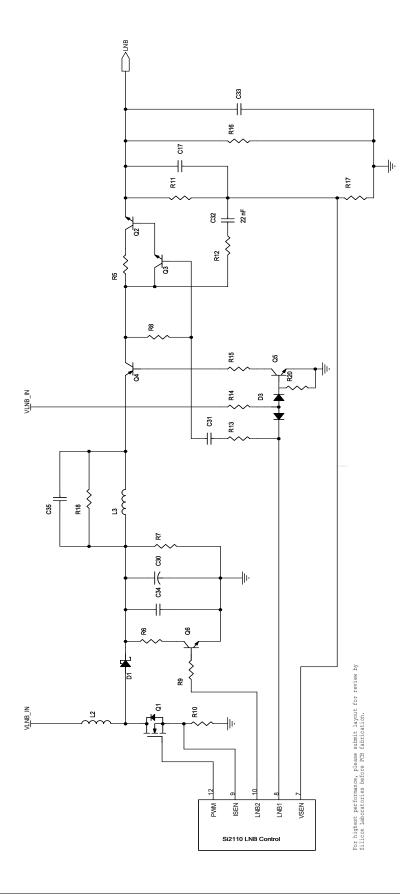

## 2. Typical Application Schematics

Figure 8. Si2107/08/09/10 Schematic

Figure 9. DiSEqC 1.x LNB Supply Circuit

Figure 10. DiSEqC 2.x LNB Supply Circuit

### 3. Bill of Materials

Table 10. Si2107/08/09/10 Bill of Materials

| Component                                 | Description                                     | Vendor               |

|-------------------------------------------|-------------------------------------------------|----------------------|

| C1,C2,C4,C6,C10,C8,C9,C13,C14,<br>C15,C16 | 0.1 μF, X7R, ±20%                               |                      |

| C5                                        | 0.01 μF, X7R, ±20%                              |                      |

| C3,C7,C11,C12                             | 33 pF, 6 V, NP0, ±10%                           |                      |

| C19,C36                                   | 33 pF, 50 V, NP0, ±10%                          |                      |

| D4                                        | Transient voltage suppressor, 20 V <sup>1</sup> | Littlefuse SMCJ20CA  |

| J1                                        | Connector, F-type, 75 Ω, 950-2150 MHz           |                      |

| R2                                        | 4.53 kΩ, 62.5 mW, ±1%                           |                      |

| X1                                        | Balun transformer                               | Anaren B0922J7575A00 |

| TC1-5 <sup>2</sup>                        | Tuning components                               |                      |

| Y1                                        | 20 MHz, 20 pF, 50 ppm, 20 $\Omega$ ESR          |                      |

| U1                                        | Si2107/08/09/10                                 | Silicon Laboratories |

#### Notes:

- 1. Transient voltage suppression device should be selected to match the surge requirements of the application.

- **2.** Tuning component values depend on balun selected and layout. Please contact Silicon Laboratories for assistance reviewing layouts and selecting matching components.

Table 11. DiSEqC 1.x LNB Supply Bill of Materials (Si2108/10 Only)

| Component | Description                                    | Vendor                      |

|-----------|------------------------------------------------|-----------------------------|

| C30       | 47 μF, 25 V, Electrolytic,± 20%                |                             |

| C31       | 0.47 μF, 25 V, X7R,± 20%                       |                             |

| C32       | 22 nF, 25 V, X7R, ± 20%                        |                             |

| C33       | 0.22 μF, 25 V, X7R, ± 20%                      |                             |

| C34       | 4.7 μF, 25 V, X7R, ± 20%                       |                             |

| D1        | CMPSH1-4, 40 V, 1 A<br>ZHCS750TA, 40 V, 750 mA | Central Semiconductor Zetex |

| D3        | MMBD1705, Dual diode, 20 V, 25 mA              | Fairchild                   |

| L2        | DR78098, 33 µH, 1.2 A, 20%<br>SD0705-330K-R-SL | Datatronic<br>ACT           |

| Q1        | ZXMN3B14<br>FDN337N                            | Zetex<br>Fairchild          |

| Q2        | FMMT618                                        | Zetex                       |

| Q3,Q5,Q6  | MMBT3904                                       | Infineon                    |

| Q4        | FMMT718                                        | Zetex                       |

| R5        | 1.3 Ω, 500 mW, ±5%                             |                             |

| R6        | 33 Ω, 250 mW, ±5%                              |                             |

| R7        | 10 kΩ, 62.5 mW, ±5%                            |                             |

| R8        | 1 kΩ, 250 mW, ±5%                              |                             |

| R9        | 680 Ω, 125 mW, ±5%                             |                             |

| R10       | 0.22 Ω, 1 W, ±5%                               |                             |

| R11       | 22 kΩ, 62.5 mW, ±1%                            |                             |

| R12,R20   | 20 kΩ, 62.5 mW, ±5%                            |                             |

| R13       | 33 Ω, 62.5 mW, ±5%                             |                             |

| R14       | 43 kΩ, 62.5 mW, ±5%                            |                             |

| R15       | 3 kΩ, 100 mW, ±5%                              |                             |

| R16       | 2 kΩ, 250 mW, ±5%                              |                             |

| R17       | 2.2 kΩ, 62.5 mW, ±1%                           |                             |

Table 12. DiSEqC 2.x LNB Supply Bill of Materials (Si2108/10 Only)

| Component | Description                                      | Vendor                         |

|-----------|--------------------------------------------------|--------------------------------|

| C17       | 1200 pF, 25 V, X7R, ± 20%                        |                                |

| C30       | 47 μF, 25 V, Electrolytic, ± 20%                 |                                |

| C31,C35   | 0.47 μF, 25 V, X7R,± 20%                         |                                |

| C32       | 22 nF, 25 V, X7R, ± 20%                          |                                |

| C33       | 0.22 μF, 25 V, X7R, ± 20%                        |                                |

| C34       | 4.7 μF, 25 V, X7R, ± 20%                         |                                |

| D1        | CMPSH1-4, 40 V, 1 A<br>ZHCS750TA, 40 V, 750 mA   | Central Semiconductor<br>Zetex |

| D3        | MMBD1705, Dual diode, 20 V, 25 mA                | Fairchild                      |

| L2        | DR78098, 33 µH, 1.2 A, 20%<br>SD0705-330K-R-SL   | Datatronic<br>ACT              |

| L3        | DR78097, 100 μH, 500 mA, 20%<br>SD0504-101K-R-SL | Datatronic<br>ACT              |

| Q1        | ZXMN3B14<br>FDN337N                              | Zetex<br>Fairchild             |

| Q2        | FMMT618                                          | Zetex                          |

| Q3,Q5,Q6  | MMBT3904                                         | Fairchild                      |

| Q4        | FMMT718                                          | Zetex                          |

| R5        | 1.3 Ω, 500 mW, ±5%                               |                                |

| R6        | 33 Ω, 250 mW, ±5%                                |                                |

| R7        | 10 kΩ, 62.5 mW, ±5%                              |                                |

| R8        | 1 kΩ, 250 mW, ±5%                                |                                |

| R9        | 680 Ω, 125 mW, ±5%                               |                                |

| R10       | 0.22 Ω, 1W, ±5%                                  |                                |

| R11       | 22 kΩ, 62.5 mW, ±1%                              |                                |

| R12,R20   | 20 kΩ, 62.5 mW, ±5%                              |                                |

| R13       | 33 Ω, 62.5 mW, ±5%                               |                                |

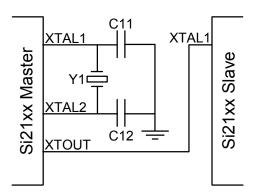

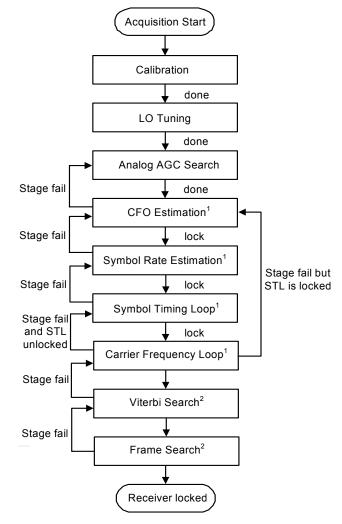

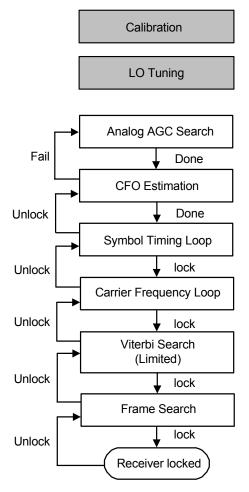

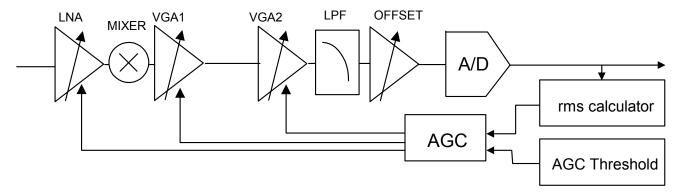

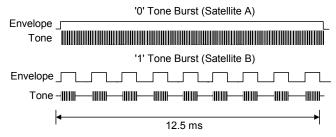

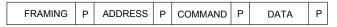

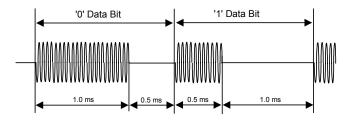

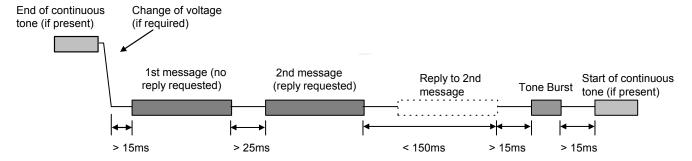

| R14       | 43 kΩ, 62.5mW, ±5%                               |                                |